Under high market demand of automobile, consumer and Information and Communication Technology (ICT) chips due to COVID-19 and development of smart driving, Japanese Semiconductor Industry is facing both chances and also challenges. In my opinion, for better future Japanese Semiconductor Industry, it is essential to achieve these two targets listed below.

- New Japanese semiconductor production and test equipment developed for satisfactory yield rate (>90%) and lower production cost when using advanced process. (Plan A1)

- Japanese firms can carry out strategic cooperation with universities and companies (Can be foreign), for development of new semiconductor devices and more advanced process (40nm below). These researches are carried out using current semiconductor production systems. As a result, relative Japanese firms also can also produce these new devices themselves. (Plan A2)

Both of Plan A1 and A2 can be carried out at the same time to help the Japanese Semiconductor as much as possible. This article discusses how strategic cooperation with suitable plans can help the Japanese Semiconductor Industry. Before explaining my views about details of strategic cooperation, let me tell you what is the importance of strategic cooperation for better future of Japanese Semiconductor firms.

For Plan A1, I have written an article entitled “Winning the Semiconductor War by a Foundry with Specific Process”. This approach aims to use patents, engineers and foundries from TPSCO to help Japanese Firms. In the future, Japanese new technologies and equipment can also be applied by X in developing new semiconductor process, with lower production cost [1], shorter lead time [2] and higher yield rate [3]. Currently, technical solutions newly developed by Japanese firms such as Jet and Flash Imprint Lithography (J-FIL) [3] and Minimal Fab [2] have much less practical experience. That results in long time preparation for them to be ready to compete with their foreign competitors such as ASML. TPSCO also currently cannot produce chips using process less than 45nm [4]. Some people suggest outsourcing more chip production to pure foundries such as TSMC and UMC.

However, on-going global shortage in wafer production capacity is due to the sharply increasing in demand of ICT (Including 5G Communication) systems and chips due to the pandemic and the recovering automobile market [5, 6, and 9]. Consumer and ICT Chips also have higher marginal profit and demand than those of automobile chips for TSMC [7, 8]. The global automobile market has been shrunk for about two years [5]. Hence, the original capacity for automobile chips has been also used by chips for consumer and ICT applications.

Due to the development of smart driving and electric vehicle, much more chips will be used by cars [5, 9]. USA, Germany and other countries have urged Taiwanese foundries to offer more wafer production capacity for automobile semiconductor [10, 11]. For major players such as Renesas, which need TSMC on production of chips using 40nm and smaller CMOS process [12, 13]. Renesas has been forced to use more production lines in Naka Fab for 40nm chip production [14]. According to some experts, including Jason Wang (CEO of UMC) and Hidetoshi Shibata (CEO of Renesas Electronics), said the shortage of automobile chips will last for at least several months, or even longer [9, 15 and 16]. Change of foundries can cause serious difficulty in on – time delivery and quality control of chip production. In the foreseeable future, China‘s military expansion against Taiwan will be another threat on stability of TSMC wafer production so the Japanese government might then have tried to invite TSMC to set up new fabs in Japan [17].

However, it is not feasible for inviting TSMC to set up new fabs in Japan. North America companies such as Qualcomm, Xilinx, AMD, Nvidia and Apple have contributed about 60% of TSMC total income [18, 19] in recent years. However, only about 5 -6% of TSMC total Income has been from Japan [18, 19]. 3 of Top 5 major manufacturers of semiconductor equipment also come from America [20, 21]. Synopsys and Cadence, two of the top three software companies offering IC Design package, also come from America.

As a result, that states the importance of Plan 1B. It helps in getting engineering knowledge of new devices and processes. That makes Japanese Semiconductor Industry know what technological requirements are essential in production of new chips and devices. By cooperation with some selected foreign companies, more technical details and process can be learnt for training of Japanese companies and engineers. After that, it will also be helpful for later modification of J-FIL and Minimal Fab. Details about cooperation between foreign firms and Japanese companies will be described in the following paragraphs. In my opinion, there are two ways.

- Renesas Electronics can work with UMC regarding the Deeply Depleted Channel™ (DDC) process, which is useful in chips with ultra low power consumption. After that, Renesas can manufacture chips using DDC technology at its fab (Plan 1B-1).

- University of Tohoku, Kioxia and Sony can also cooperate for SOT- MRAM, used in cache memory of advanced CIS and memory chips (Plan 1B-2).

For Plan 1B-1, UMC gradually licenses its 28nm and below semiconductor process platform to Renesas. After Renesas has feminized with 28nm semiconductor process platform, UMC then outsources the development of automobile grade DDC CMOS process (40nm and below) to Renesas. Finally, the results of DDC technology development will be shared by both UMC and Renesas. A Win – Win situation can be achieved between UMC and Renesas.

- UMC also needs to focus its effort and resources on modification of 14nm CMOS Process. For foundries, more micro – refined process is more profitable than that of less micro – refined process. Let‘s take TSMC as an example.

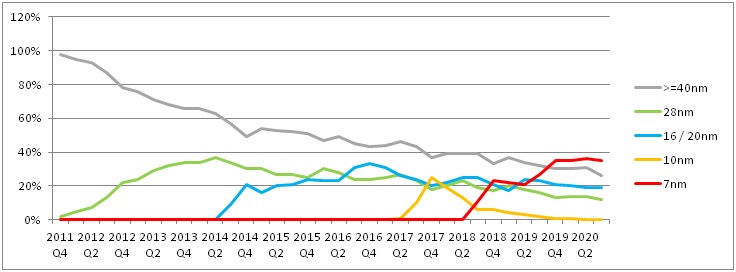

According to Chart 1, if a newer process has higher revenue than others, it will take shorter time to achieve a specific sufficient percentage (In this article, 33% is selected as reference). For TSMC 28nm CMOS Process, it takes 27 months to contribute about 33% of total wafer revenue at a later quarter. However, it only took 18 months for TSMC 7nm CMOS Process to achieve the same target. Higher wafer revenue of for TSMC 7nm CMOS Process is due to the global wafer foundry market has become a duopoly. Only Samsung and TSMC have enough capital and technical assents to invest in more micro-refined semiconductor process. According to the third quarter of 2020, 20nm and below CMOS process has contributed over than 50% of TSMC total income [8]. If UMC staff can focus on its 14nm CMOS process modification earlier, which is more profitable, its operation efficiency and R&D progress can be further improved.

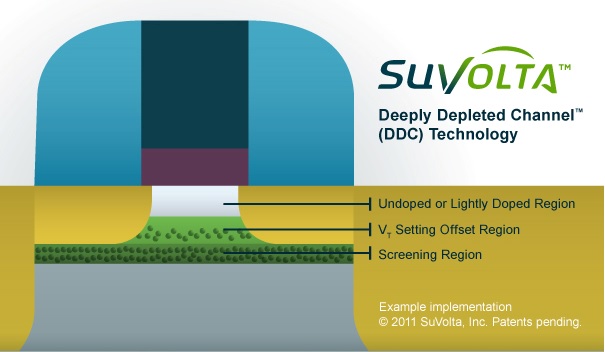

- It results in more stable fab network and more advantage in R&D of Renesas chips. Renesas will have more advantage in developing chips. Currently, Renesas‘s SOTB Process has been developed due to its ultra low power consumption [22]. However, when the SOTB process is further miniaturized from 65nm, thinner wires result in larger leakage current. Finally, 28nm SOTB will have no technical advantage over 28nm FD-SOI because their leakage current is close to each other [23]. In my opinion, DDC is a better alternative for Renesas because it slightly modifies conventional planar bulk CMOS transistors by changing the single CMOS channel layer into three functional layers [26, 27]. The diagram of a DDC transistor is shown in Figure 2.

From Figure 2, the features of three layers within channel layer are shown below.

Top layer (Undoped or lightly Doped): Enable Vdd scaling and transistors driving larger effective current [26, 27]

Middle layer (Vth setting and Vth variability suppression of transistors): It aims to better yield (For random dopant fluctuation (RDF) reduction [27]) and identical speed of all transistors [26]) without degrading channel mobility [26, 27].

Bottom layer (Screening): Body for its depleted behavior (For achieving many merits compared to planar bulk CMOS [24]) as that of SOTB transistor and further dynamic Vth variability suppression through biasing [26, 27]

Further power saving and temperature effect minimization can be achieved by dynamic body biasing on the body layer, underneath of the three channel layers of Figure 2 [25, 28]. DDC PowerShrink technology enables power saving by 50% and reduction of supply voltage (Vdd) by 30% [25, 26, 28] while original clock speed can also be maintained. Standard planar bulk CMOS design and manufacturing infrastructure can be slightly modified to produce chips using DDC PowerShrink transistors [25, 26]. Expected features of DDC PowerShrink technology has been obtained using a 28nm transistor (Effects of DDC on 14nm CMOS process has been confirmed by simulation [28]). As a result, DDC can become a better alternative apart from FD-SOI and Fin-FET which require expensive investment in special process and manufacturing systems [25, 28]. DDC PowerShrink has been firstly adopted at a mass production of Fujitsu Semiconductor MB86S22AA, an image processor on 2013 (Source: https://www.fujitsu.com/jp/group/fsl/en/documents/about/resources/news/press-releases/2013/20130904-2e.pdf).By adopting DDC PowerShrink technology, Renesas‘s chips can achieve ultra low power consumption and lower cost.

- It will be helpful to feminize clients with advantages of new technology developed by Renesas and UMC. If DDC CMOS technology can be adopted by Renesas, more Japanese clients can be attracted to use DDC PowerShrink technology and outsource their chip production to UMC.

- Some people may think that Renesas can also become another competitor of UMC after it can use 28nm CMOS process to manufacture chips. However, in my opinion, UMC and Renesas can achieve a Win – Win situation by my idea.

- Renesas can share the results of R&D with UMC and its expenditure can be shared with UMC and INCJ

- UMC does not compete with its clients because UMC just have revenues by its wafer foundry service. However, Renesas competes with many other semiconductor firms, which may be clients of UMC.

- UMC has more micro-refined process technology (14nm currently) than Renesas (40nm minimum currently [29])

By strategic cooperation with UMC, Renesas can co-develop and produce chip itself using DDC ultra low power. Apart from sharing DDC technologies with Renesas, UMC also can utilize its resource on other useful technologies.

After Plan 1B-1, the paragraphs below will explain Plan 1B-2.

For Plan 1B-2, Because of large demand of CIS from smart devices and CCTVs, Sony can get large amount of income from their CIS products [30, 31]. Sony even has invested more on R&D of CIS [31, 32]. Samsung, second major supplier of CIS, has also started the transformation of its old fabs, for producing more new CIS [31, 32]. It shows that CIS market is profitable with satisfactory margin profit. It can attract Sony to invest more money on CIS development. Sony has developed the first 3-Layer, 960 fps CMOS Image Sensors (CIS) for [33]. This CIS enables super slow motion Full HD (1920 x 1080 pixels, up to 960 fps) movies and high speed readout of pixel data (19.3M pixel in 1/120 second). This image sensor also requires DRAM for temporarily storing the high speed pixel data [33] during taking super slow motion movie (in Full HD). However, for further development of CIS, it is essential for CIS manufacturers to deal with higher pixel data rate for applications such as 8K filming, gaming and sporting applications, which need high Frame per Second (FPS) videos for eliminating motion blur and maintaining the video quality at super slow motion screening [34]. Due to increasing number of pixels of CIS, more micro refined process also has been adopted in development of CIS [34]. As a result, a type of new memory for temporary storage of pixel data must have better scalability and higher speed than those of DRAM. STT-MRAM is being a candidate of new generic memory due to its capability of downscaling [36], non-volatility [35, 36, 37, 38], lower power consumption [35, 36, 37], less complexity [37], immune to radiation [37], higher density [35], number of rewrites [35] and faster R/W speed [35, 36, 37, 38].

However, the write speed of STT-MRAM is currently not fast enough to be next generation of cache memory due to its design [35, 39, and 40]. The read and write operations are controlled by the same path [39], which results in larger write latency and slower write speed. For further higher writing speed, SOT-MRAM has been developed for new L1 / L2 cache memory. Researchers of Tohoku University has also developed SOT-MRAM memory cell using standard 55nm CMOS process, with demonstration of sub-ns write speed and semiconductor integration process for SOT-MRAM, enabling thermal tolerance against 400 Degrees annealing [40] during standard semiconductor production. Sony has used Micron DRAM as temporary storage of pixel data [33] but SOT-MRAM can be used as temporary memory for Sony CIS in the future.

Kioxia can also produce SOT-MRAM for Sony CIS and its own memory products, used as high speed memory in both caches and solid state disk (SSD). Due to its high speed, high density and other advantages, Kioxia will become a potential strong opponent of current DRAM main manufacturers.

Finally, this article has shown my ideas of suitable plans of strategic cooperation, which are essential for future success of the Japanese Semiconductor Industry. I also will be glad if my ideas and opinion can help Japanese Semiconductor Firms to strike a good balance between cost control and more stable supply of their chips by extra investment on their fabs.

References

[1] cnt.canon.com/technology/j-fil-overview/

[2] https://report.nat.gov.tw/ReportFront/PageSystem/reportFileDownload/C10603764/001

[3] https://www.nature.com/articles/micronano201775.pdf

[4] https://tpsemico.com/process_technology_offerings/

[5] https://www.bnext.com.tw/article/61163/car-chip-global-problem?utm_source=dable

[6] https://money.udn.com/money/story/5612/5240010?from=edn_catehotlist_story

[7] https://ctee.com.tw/news/stock/412893.html

[8] TSMC Financial Report https://investor.tsmc.com/chinese/quarterly-results

[9] https://www.moneyweekly.com.tw/ArticleData/Info/說解財經大小事/52325/

[13] https://pr.tsmc.com/chinese/news/1903

[14] https://cn.nikkei.com/industry/itelectric-appliance/43647-2021-01-29-08-48-59.html/?n_cid=NKCHA014

[16] https://news.cnyes.com/news/id/4562881

[17] https://www.bnext.com.tw/article/61224/japan-semiconductor-tsmc?utm_source=dable

[18] https://finance.technews.tw/2019/02/23/tsmc-2018-market/

[19] https://investor.tsmc.com/static/annualReports/2019/chinese/pdf/c_all.pdf

[20] https://www.vlsiresearch.com/the-chip-insider/semiconductor-equipment-suppliers-growth-database-2019

[21] https://www.vlsiresearch.com/public/cms_pdf_upload/tci190314/tci190314.htm

[22] https://www.renesas.com/us/en/solutions/key-technology/sotb/merit.html

[23] http://eetimes.jp/ee/articles/1811/20/news041_2.html

[24] https://www.soitec.com/en/products/fd-soi

[25] https://www.printedelectronicsworld.com/articles/3471/suvoltas-innovative-powershrink

[27] https://www.theregister.com/Print/2011/12/07/suvolta_ddc_transistor/

[28] https://news.mynavi.jp/article/20110616-powershrink/

[29] https://www.sangyo-times.jp/article.aspx?ID=3138

[31] https://udn.com/news/story/7240/4680936

[32] http://www.businesskorea.co.kr/news/articleView.html?idxno=56553

[33] https://fuse.wikichip.org/news/763/iedm-2017-sonys-3-layer-stacked-cmos-image-sensor-technology/

[34] https://camerajabber.com/buyersguides/which-cameras-shoot-4k-at-120fps/

[35] https://pc.watch.impress.co.jp/docs/column/semicon/1145577.html

[36] https://news.cnyes.com/news/id/4468534

[37] https://www.spinmemory.com/spinuploads/2018/07/IT-ProPortal-eprint-MRAM_plain_v2.pdf

[38] https://www.eettaiwan.com/20190314nt22-most-mram/

[39] https://www.digitimes.com.tw/col/article.asp?id=1017

https://www.digitimes.com.tw/col/article.asp?id=1018

[40] https://www.tohoku.ac.jp/en/press/sot_with300mm_si_cmos_technology.html